The KV10 is an FPGA implementation of the DEC PDP-10 processor very much in the style of Dave Conroy's PDP-10/X . Like Dave's design, I'm aiming this specifically to run ITS.

I started writing this is 2011 in a language called Balsa, an HDL designed for doing asynchronous logic. Given that the KA10 was async (though of a different style), this seemed appropriate and interesting. It wasn't a good match for FPGAs though, which were going to be my way of realizing my design, and so I switched over to Verilog. I've since re-written the whole thing three times, starting with a state-machine design and ending up micro-coded. I'm still interested in the idea of an asynchronous design though I don't know that I'll ever get there.

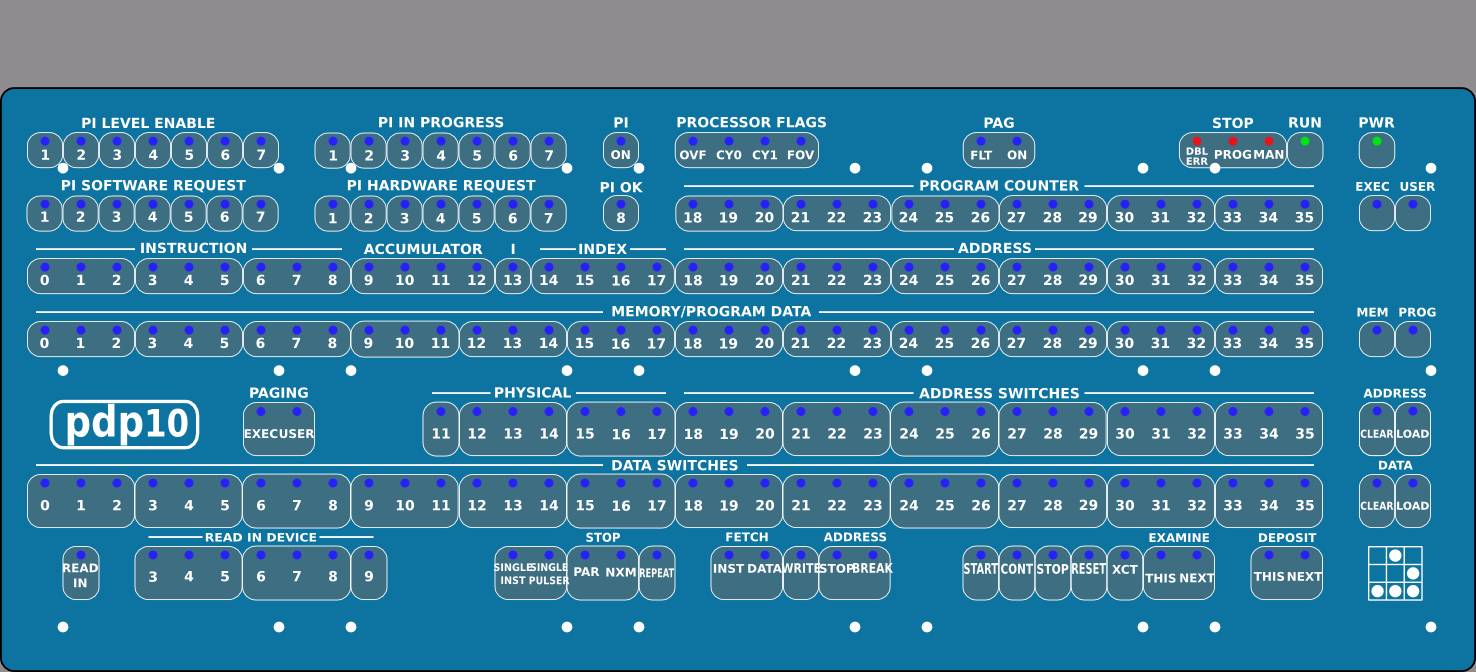

My initial idea for a console was a capacitive touch-panel modeled after the KI10.

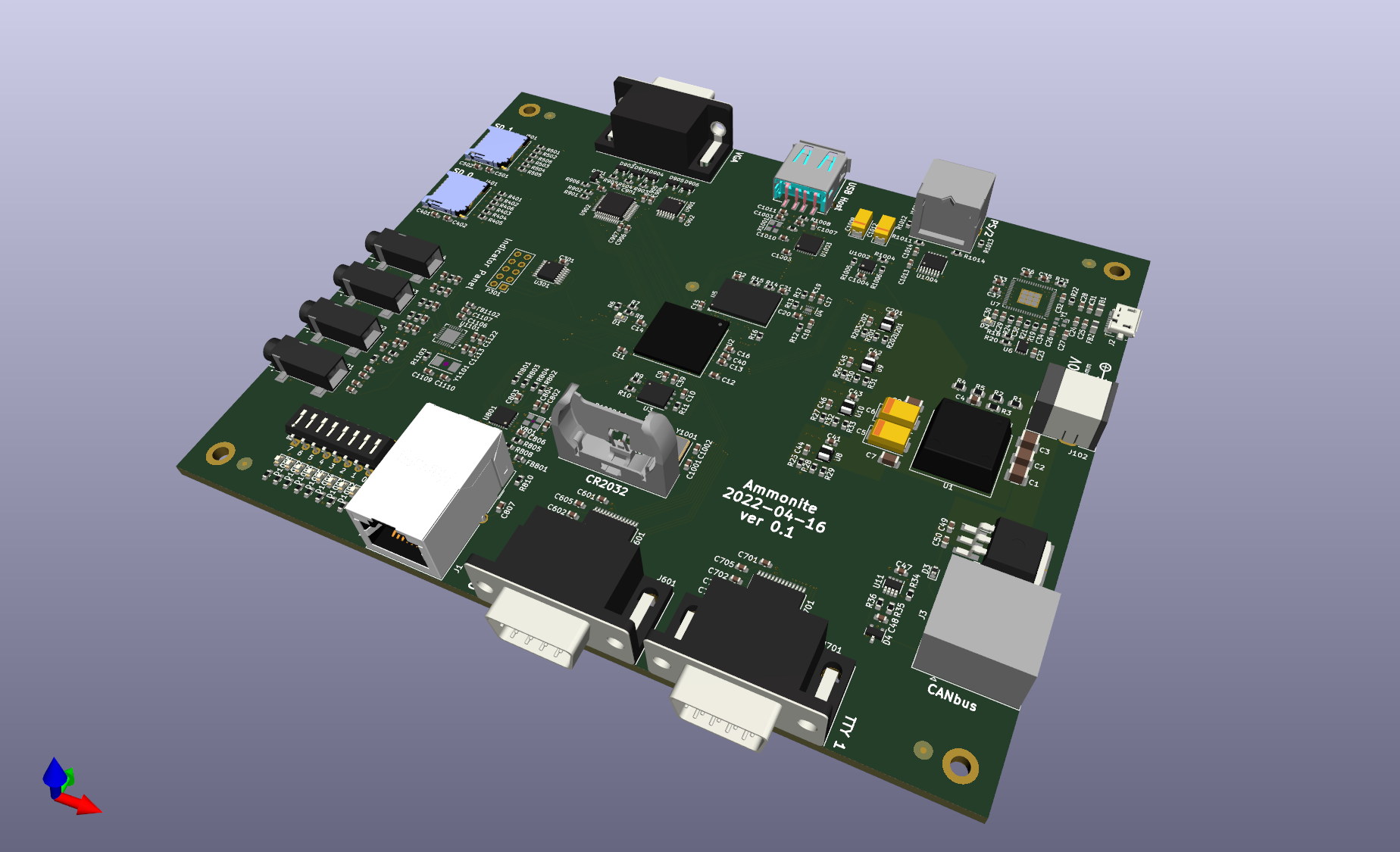

This would use five of these circuit boards behind the overlay. Here is a 3D image of the board and the schematic.

However, Oscar is working on his PiDP-10 console (KA10 replica) so I'm thinking to just interface with that instead.

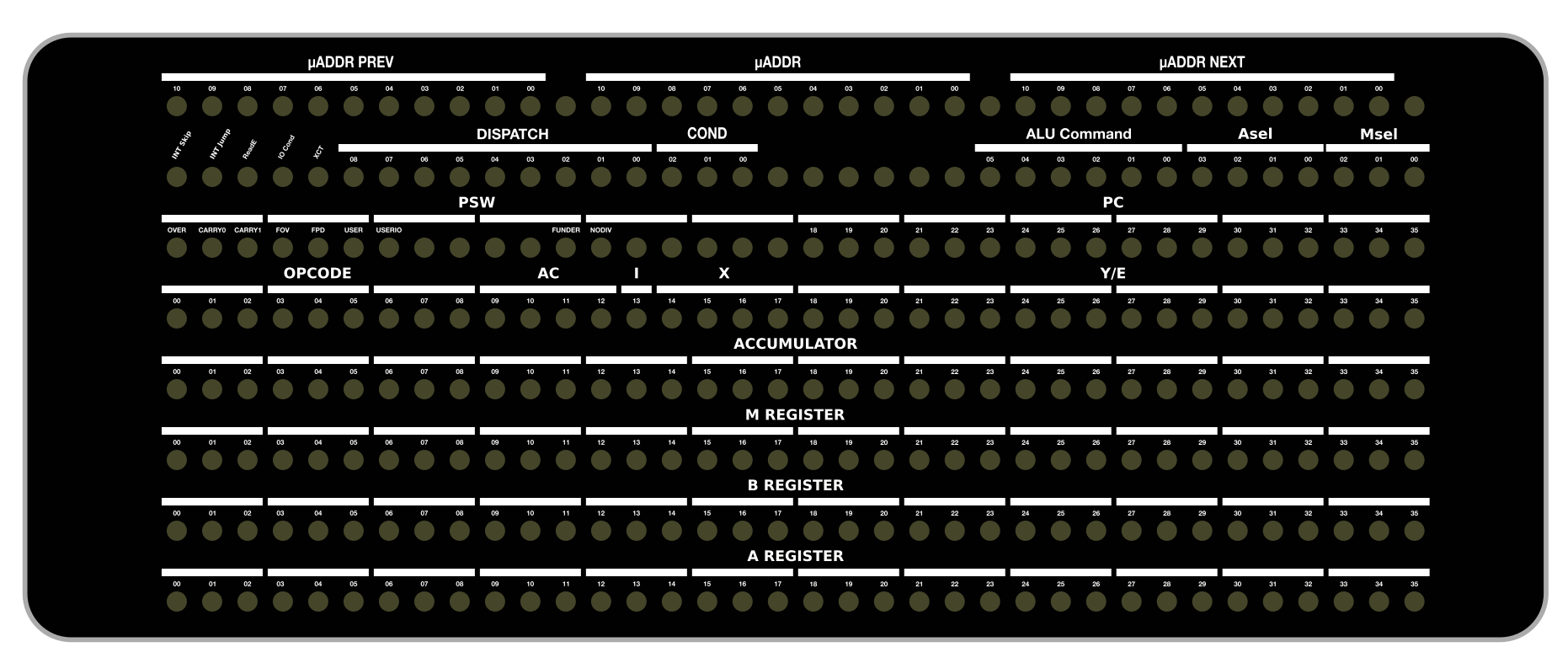

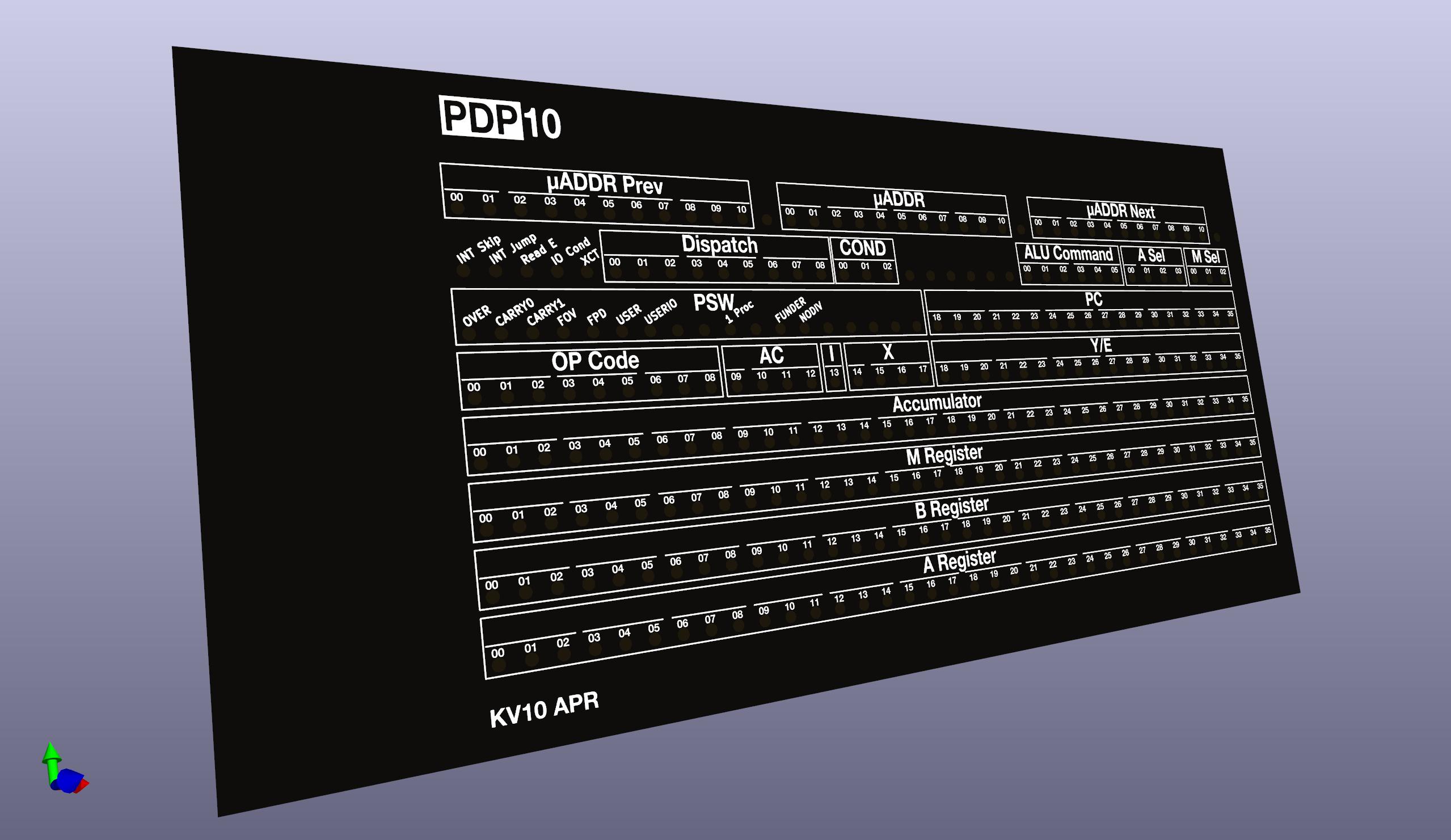

If that's not enough blinkenlights, could add an indicator panel for the APR.

Here's a start at a Processor Reference Manual.

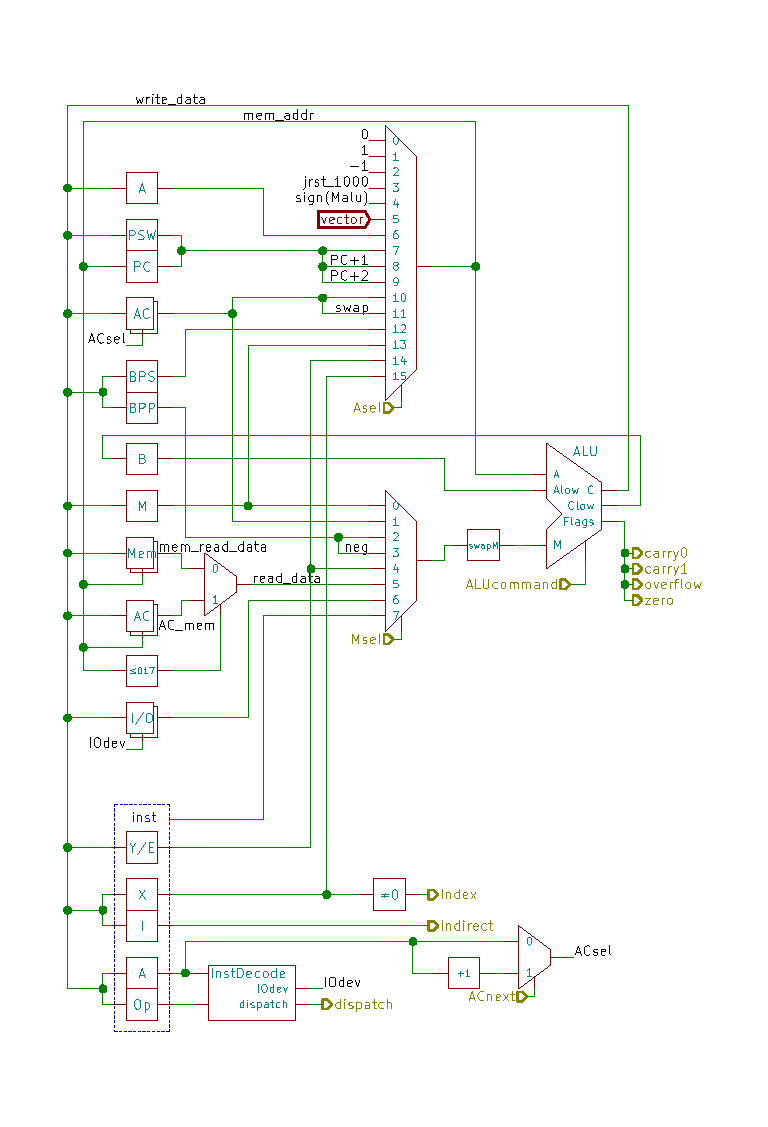

The datapaths for the processor. It's currently running (in a Verilog simulator) and passing diagnostics for all of the user-mode instructions except for floating-point. The code is up on GitHub.

Realizing this needs an FPGA board. None of the ones I can find to buy seem to really include the I/O devices that I'm looking for and so the Ammonite board is my idea of what I want.